## VSI OpenVMS

## Alpha Guide to Upgrading Privileged-Code Applications

Document Number: DO-DUPGAP-01A

Publication Date: May 2024

Operating System and Version: VSI OpenVMS IA-64 Version 8.4-1H1 or higher VSI OpenVMS Alpha Version 8.4-2L1 or higher

#### Alpha Guide to Upgrading Privileged-Code Applications

VMS Software

Copyright © 2024 VMS Software, Inc. (VSI), Boston, Massachusetts, USA

#### Legal Notice

Confidential computer software. Valid license from VSI required for possession, use or copying. Consistent with FAR 12.211 and 12.212, Commercial Computer Software, Computer Software Documentation, and Technical Data for Commercial Items are licensed to the U.S. Government under vendor's standard commercial license.

The information contained herein is subject to change without notice. The only warranties for VSI products and services are set forth in the express warranty statements accompanying such products and services. Nothing herein should be construed as constituting an additional warranty. VSI shall not be liable for technical or editorial errors or omissions contained herein.

HPE, HPE Integrity, HPE Alpha, and HPE Proliant are trademarks or registered trademarks of Hewlett Packard Enterprise.

| Preface                                                                                                     | vii |

|-------------------------------------------------------------------------------------------------------------|-----|

| 1. About VSI                                                                                                | vii |

| 2. Intended Audience                                                                                        | vii |

| 3. Document Structure                                                                                       |     |

| 4. Related Documents                                                                                        |     |

| 5. VSI Encourages Your Comments                                                                             |     |

| 6. OpenVMS Documentation                                                                                    |     |

| 7. Typographical Conventions                                                                                |     |

| Chapter 1. Introduction                                                                                     |     |

| 1.1. Quick Description of OpenVMS Alpha 64-Bit Virtual Addressing                                           |     |

|                                                                                                             |     |

| 1.2. Quick Description of OpenVMS Alpha Kernel Threads                                                      |     |

| <ul><li>1.3. Quick Description of OpenVMS Industry Standard 64</li><li>1.4. How to Use This Guide</li></ul> |     |

|                                                                                                             |     |

| Chapter 2. Upgrading Privileged Software to OpenVMS Alpha Version 7.0                                       |     |

| 2.1. Recommendations for Upgrading Privileged-Code Applications                                             |     |

| 2.1.1. Summary of Infrastructure Changes                                                                    | 3   |

| 2.1.2. Changes Not Identified by Warning Messages                                                           | 4   |

| 2.2. I/O Changes                                                                                            |     |

| 2.2.1. Impact of IRPE Data Structure Changes                                                                |     |

| 2.2.2. Impact of MMG_STD\$IOLOCK, MMG_STD\$UNLOCK Changes                                                   |     |

| 2.2.2.1. Direct I/O Functions                                                                               |     |

| 2.2.3. Impact of MMG_STD\$SVAPTECHK Changes                                                                 | . 8 |

| 2.2.4. Impact of PFN Database Entry Changes                                                                 | . 9 |

| 2.2.5. Impact of IRP Changes                                                                                | . 9 |

| 2.3. General Memory Management Infrastructure Changes                                                       |     |

| 2.3.1. Location of Process Page Tables                                                                      | . 9 |

| 2.3.2. Interpretation of Global and Process Section Table Index                                             | 10  |

| 2.3.3. Location of Process and System Working Set Lists                                                     | 10  |

| 2.3.4. Size of a Working Set List Entry                                                                     |     |

| 2.3.5. Location of Page Frame Number (PFN) Database                                                         | 10  |

| 2.3.6. Format of PFN Database Entry                                                                         | 11  |

| 2.3.7. Process Header WSLX and BAK Arrays                                                                   | 11  |

| 2.3.8. Free S0/S1 System Page Table Entry List                                                              | 11  |

| 2.3.9. Location of the Global Page Table                                                                    | 11  |

| 2.3.10. Free Global Page Table Entry List                                                                   |     |

| 2.3.11. Region Descriptor Entries (RDEs)                                                                    | 12  |

| 2.4. Kernel Threads Changes                                                                                 |     |

| 2.4.1. The CPU\$L_CURKTB Field                                                                              |     |

| 2.4.2. Mutex Locking                                                                                        | 12  |

| 2.4.3. Scheduling Routines                                                                                  |     |

| 2.4.4. New MWAIT State                                                                                      | 13  |

| 2.4.5. System Services Dispatching                                                                          |     |

| 2.4.6. Asynchronous System Traps (ASTs)                                                                     |     |

| 2.4.7. TB Invalidation and Macros                                                                           |     |

| 2.4.8. New PCB/KTB Fields                                                                                   |     |

| 2.4.9. CTL\$AL_STACK and CTL\$AL_STACKLIM                                                                   |     |

| 2.4.10. Floating-Point Register and Execution Data Blocks (FREDs)                                           |     |

| 2.5. Registering Images That Have Version Dependencies                                                      |     |

| 2.5.1. Version Identification (ID) Number Change to Three Subsystems                                        | 17  |

| Chapter 3. Replacements for Removed Privileged Symbols                                                      | 19  |

| 3.1. Removed Date Structure Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2. Removed Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                                                                                                                       |

| 3.3. Removed Macros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                                                       |

| 3.3.1. Removed MACRO-32 Macros Formerly in SYS\$LIBRARY:LIB.MLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                                                                       |

| 3.3.2. C Header Files Removed From SYS\$LIBRARY:SYS\$LIB_C.TLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                                                                                                                       |

| 3.4. Removed System Data Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29                                                                                                                                                       |

| Chapter 4. Modifying Device Drivers to Support 64-Bit Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                                                                                       |

| 4.1. Recommendations for Modifying Device Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                          |

| 4.2. Mixed Pointer Environment in C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                          |

| 4.3. \$QIO Support for 64-Bit Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                          |

| 4.4. Declaring Support for 64-Bit Addresses in Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                          |

| 4.4.1. Drivers Written in C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                          |

| 4.4.2. Drivers Written in MACRO-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                          |

| 4.4.3. Drivers Written in BLISS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |

| 4.5. I/O Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37                                                                                                                                                       |

| 4.5.1. Simple Buffered I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                                                                       |

| 4.5.2. Direct I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39                                                                                                                                                       |

| 4.5.3. Direct I/O Buffer Map (DIOBM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39                                                                                                                                                       |

| 4.5.4. 64-Bit AST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                          |

| 4.5.5. 64-Bit ACB Within the IRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                                                                                                       |

| 4.5.6. I/O Function Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                                                                                                                                                       |

| 4.6. 64-Bit Support in Example Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                                                       |

| 4.6.1. Example: Declaring 64-Bit Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                                                                                                                                       |

| 4.6.2. Example: Declaring 64-Bit Buffered I/O Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| 4.6.3. Example: Changes to LR\$WRITE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| 4.6.4. Example: Changes to LR\$SETMODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                                                                       |

| 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                          |

| 4.6.5. Example: Changes to LR\$STARTIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                          |

| 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45                                                                                                                                                       |

| 4.6.5. Example: Changes to LR\$STARTIO<br>Chapter 5. Modifying User-Written System Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br><b> 47</b>                                                                                                                                         |

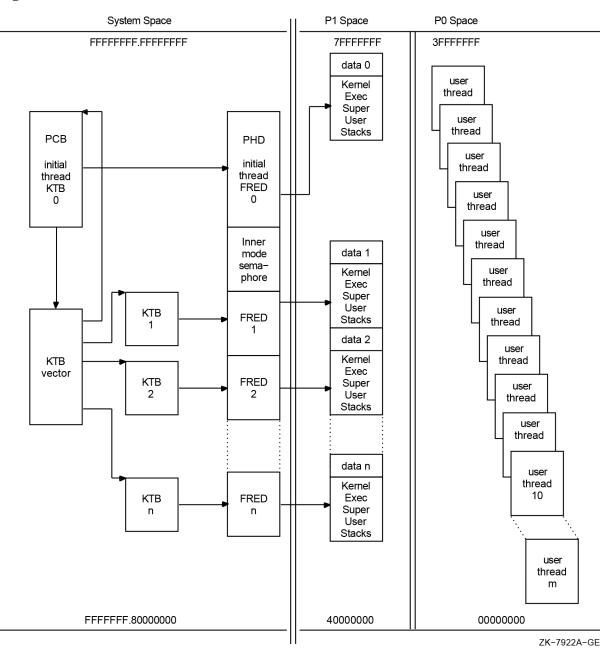

| 4.6.5. Example: Changes to LR\$STARTIO<br>Chapter 5. Modifying User-Written System Services<br>Chapter 6. Kernel Threads Process Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45<br>47<br>51                                                                                                                                           |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51                                                                                                                                     |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>51                                                                                                                               |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52                                                                                                                               |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52                                                                                                                         |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53                                                                                                             |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br><b> 47</b><br><b> 51</b><br>51<br>52<br>52<br>52<br>53<br>53                                                                                       |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>53<br>53<br>53                                                                                                       |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br><b></b> 47<br><b></b> 51<br>51<br>52<br>52<br>53<br>53<br>53<br>53                                                                                 |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>54                                                                                     |

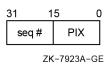

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li> <li>6.1. Process Control Blocks (PCBs) and Process Headers (PHDs)</li> <li>6.1.1. Effect of a Multithreaded Process on the PCB and PHD</li> <li>6.2. Kernel Thread Blocks (KTBs)</li> <li>6.2.1. KTB Vector</li> <li>6.2.2. Floating-Point Registers and Execution Data Blocks (FREDs)</li> <li>6.2.3. Kernel Threads Region</li> <li>6.2.4. Per-Kernel Thread Stacks</li> <li>6.2.5. Per-Kernel Thread Data Cells</li> <li>6.2.6. Layout of the Per-Kernel Thread</li> <li>6.2.7. Summary of Process Data Structures</li> <li>6.3. Process Identifiers (PIDs)</li> </ul>                                                                                                                                                                                                                                                                                                           | 45<br><b> 47</b><br><b> 51</b><br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>54<br>55                                                                     |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56                                                                   |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>57                                                             |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>57                                                             |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>54<br>55<br>56<br>57<br>57                                                       |

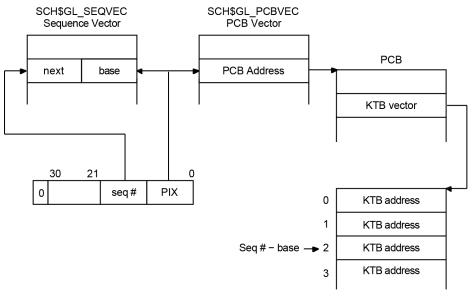

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>57<br>57<br>57<br>59                                           |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>57<br>57<br>59<br>59                                                 |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li> <li>6.1. Process Control Blocks (PCBs) and Process Headers (PHDs)</li> <li>6.1.1. Effect of a Multithreaded Process on the PCB and PHD</li> <li>6.2. Kernel Thread Blocks (KTBs)</li> <li>6.2.1. KTB Vector</li> <li>6.2.2. Floating-Point Registers and Execution Data Blocks (FREDs)</li> <li>6.2.3. Kernel Thread Stacks</li> <li>6.2.4. Per-Kernel Thread Stacks</li> <li>6.2.5. Per-Kernel Thread Data Cells</li> <li>6.2.6. Layout of the Per-Kernel Thread</li> <li>6.2.7. Summary of Process Data Structures</li> <li>6.3. Process Identifiers (PIDs)</li> <li>6.3.1. Multithread Effects on the PID</li> <li>6.3.2. Range Checking and Sequence Vectors</li> <li>6.4. Process Status Bits</li> </ul>                                                                                                                                                                       | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>57<br>57<br>59<br>60                                     |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li> <li>6.1. Process Control Blocks (PCBs) and Process Headers (PHDs)</li> <li>6.1.1. Effect of a Multithreaded Process on the PCB and PHD</li> <li>6.2. Kernel Thread Blocks (KTBs)</li> <li>6.2.1. KTB Vector</li> <li>6.2.2. Floating-Point Registers and Execution Data Blocks (FREDs)</li> <li>6.2.3. Kernel Threads Region</li> <li>6.2.4. Per-Kernel Thread Stacks</li> <li>6.2.5. Per-Kernel Thread Data Cells</li> <li>6.2.6. Layout of the Per-Kernel Thread</li> <li>6.2.7. Summary of Process Data Structures</li> <li>6.3. Process Identifiers (PIDs)</li> <li>6.3.1. Multithread Effects on the PID</li> <li>6.3.2. Range Checking and Sequence Vectors</li> <li>6.4. Process Status Bits</li> </ul> Appendix A. Data Structure Changes                                                                                                                                   | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>57<br>57<br>57<br>59<br>60<br>60 |

| <ul> <li>4.6.5. Example: Changes to LR\$STARTIO</li> <li>Chapter 5. Modifying User-Written System Services</li> <li>Chapter 6. Kernel Threads Process Structure</li> <li>6.1. Process Control Blocks (PCBs) and Process Headers (PHDs)</li> <li>6.1.1. Effect of a Multithreaded Process on the PCB and PHD</li> <li>6.2. Kernel Thread Blocks (KTBs)</li> <li>6.2.1. KTB Vector</li> <li>6.2.2. Floating-Point Registers and Execution Data Blocks (FREDs)</li> <li>6.2.3. Kernel Threads Region</li> <li>6.2.4. Per-Kernel Thread Stacks</li> <li>6.2.5. Per-Kernel Thread Data Cells</li> <li>6.2.6. Layout of the Per-Kernel Thread</li> <li>6.2.7. Summary of Process Data Structures</li> <li>6.3. Process Identifiers (PIDs)</li> <li>6.3.1. Multithread Effects on the PID</li> <li>6.3.2. Range Checking and Sequence Vectors</li> <li>6.4. Process Status Bits</li> </ul> Appendix A. Data Structure Changes <ul> <li>A.1. Pointer Size Conventions</li> <li>A.2. Buffer Object Descriptor (BOD)</li> <li>A.3. Buffered I/O (BUFIO)</li> </ul> | 45<br>47<br>51<br>51<br>52<br>52<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>57<br>57<br>59<br>60<br>62                               |

| A.7. Function Decision Table (FDT)                              | 68  |

|-----------------------------------------------------------------|-----|

| A.8. I/O Request Packet (IRP)                                   | 68  |

| A.9. I/O Request Packet Extension (IRPE)                        |     |

| A.10. Process Header (PHD)                                      |     |

| A.11. SCSI-2 Diagnose Buffer (S2DGB)                            | 76  |

| A.12. VMS Communications Request Packet (VCRP)                  | 76  |

| Appendix B. I/O Support Routine Changes                         | 79  |

| B.1. ACP_STD\$READBLK and ACP_STD\$WRITEBLK                     |     |

| B.2. EXE_STD\$ALLOC_BUFIO_32, EXE_STD\$ALLOC_BUFIO_64           | 79  |

| B.3. EXE_STD\$ALLOC_DIAGBUF                                     | 80  |

| B.4. EXE_STD\$LOCK_ERR_CLEANUP                                  |     |

| B.5. EXE_STD\$MODIFY, EXE_STD\$READ, EXE_STD\$WRITE             | 82  |

| B.6. EXE_STD\$MODIFYLOCK, EXE_STD\$READLOCK, EXE_STD\$WRITELOCK | 83  |

| B.6.1. CALL_xLOCK and CALL_xLOCK_ERR Macros                     | 84  |

| B.7. EXE_STD\$READCHK and EXE_STD\$WRITECHK                     | 84  |

| B.7.1. CALL_xCHK and CALL_xCHKR Macros                          | 84  |

| B.8. EXE_STD\$SETCHAR and EXE_STD\$SETMODE                      | 84  |

| B.9. IOC_STD\$CREATE_DIOBM                                      | 85  |

| B.10. IOC_STD\$FILL_DIOBM                                       | 86  |

| B.11. IOC_STD\$PTETOPFN                                         | 88  |

| B.12. IOC_STD\$RELEASE_DIOBM                                    |     |

| B.13. IOC_STD\$SIMREQCOM, IOC\$SIMREQCOM                        |     |

| B.13.1. CALL_SIMREQCOM Macro                                    |     |

| B.13.2. IOC\$SIMREQCOM                                          |     |

| B.14. IOC_STD\$SVAPTE_IN_BUF                                    | 89  |

| B.15. IOC_STD\$VA_TO_PA                                         |     |

| B.16. MMG_STD\$GET_PTE_FOR_VA                                   |     |

| B.17. MMG_STD\$IOLOCK, MMG\$IOLOCK, MMG_STD\$IOLOCK_BUF         |     |

| B.17.1. CALL_IOLOCK Macro                                       |     |

| B.18. MMG_STD\$UNLOCK, MMG\$UNLOCK, MMG_STD\$IOUNLOCK_BUF       |     |

| B.18.1. CALL_UNLOCK Macro                                       |     |

| B.19. MMG_STD\$SVAPTECHK, MMG\$SVAPTECHK                        | 96  |

| Appendix C. Kernel Threads Routines and Macros                  | 99  |

| EXE\$CVT_IPID_TO_KTB Routine                                    | 99  |

| EXE\$CVT_EPID_TO_KTB Routine                                    | 100 |

| GET_CURKTB Macro                                                |     |

| CVT_IPID_TO_PCB_KTB Macro                                       |     |

| CVT_IPID_TO_KTB Macro                                           | 103 |

# Preface

This document describes reference information for System Management utilities used with the OpenVMS Alpha operating system.

## 1. About VSI

VMS Software, Inc. (VSI) is an independent software company licensed by Hewlett Packard Enterprise to develop and support the OpenVMS operating system.

## 2. Intended Audience

This guide is intended for system programmers who use privileged-mode interfaces in their applications.

## 3. Document Structure

This manual is organized as follows:

- Chapter 1 describes how to use this guide.

- Chapter 2 and Chapter 3 describe the infrastructure changes that might affect privileged-code applications and provides guidelines for upgrading them to OpenVMS Alpha Version 7.0.

- Chapter 4, Chapter 5, and Chapter 6 describe the changes that can be made to customer-written system services and device drivers to support 64-bit addresses and kernel threads.

- Appendix A, Appendix B, and Appendix C contain descriptions of I/O routines, I/O data structures, kernel threads routines, and kernel threads macros.

## 4. Related Documents

- OpenVMS Alpha Guide to 64-Bit Addressing and VLM Features

- VSI OpenVMS Programming Concepts Manual

- VSI OpenVMS Record Management Services Reference Manual

- VSI OpenVMS System Services Reference Manual: A-GETUAI and VSI OpenVMS System Services Reference Manual: GETUTC-Z

## 5. VSI Encourages Your Comments

You may send comments or suggestions regarding this manual or any VSI document by sending electronic mail to the following Internet address: <docinfo@vmssoftware.com>. Users who have VSI OpenVMS support contracts through VSI can contact <support@vmssoftware.com> for help with this product.

## 6. OpenVMS Documentation

The full VSI OpenVMS documentation set can be found on the VMS Software Documentation webpage at <u>https://docs.vmssoftware.com</u>.

## 7. Typographical Conventions

The following conventions are used in this manual:

| Convention Meaning |                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | A horizontal ellipsis in examples indicates one of the following possibilities:                                                                                                                                                                                                                                                        |  |

|                    | • Additional optional arguments in a statement have been omitted.                                                                                                                                                                                                                                                                      |  |

|                    | • The preceding item or items can be repeated one or more times.                                                                                                                                                                                                                                                                       |  |

|                    | • Additional parameters, values, or other information can be entered.                                                                                                                                                                                                                                                                  |  |

| :                  | A vertical ellipsis indicates the omission of items from a code example or<br>command format; the items are omitted because they are not important to the<br>topic being discussed.                                                                                                                                                    |  |

| ()                 | In command format descriptions, parentheses indicate that you must enclose choices in parentheses if you specify more than one.                                                                                                                                                                                                        |  |

| []                 | In command format descriptions, brackets indicate optional choices. You can choose one or more items or no items. Do not type the brackets on the command line. However, you must include the brackets in the syntax for OpenVMS directory specifications and for a substring specification in an assignment statement.                |  |

| 1                  | In command format descriptions, vertical bars separate choices within<br>brackets or braces. Within brackets, the choices are optional; within braces,<br>at least one choice is required. Do not type the vertical bars on the command<br>line.                                                                                       |  |

| { }                | In command format descriptions, braces indicate required choices; you must choose at least one of the items listed. Do not type the braces on the command line.                                                                                                                                                                        |  |

| bold text          | This typeface represents the name of an argument, an attribute, or a reason.                                                                                                                                                                                                                                                           |  |

| italic text        | Italic text indicates important information, complete titles of manuals, or variables. Variables include information that varies in system output (Internal error <i>number</i> ), in command lines (/PRODUCER= <i>name</i> ), and in command parameters in text (where <i>dd</i> represents the predefined code for the device type). |  |

| UPPERCASE TEXT     | Uppercase text indicates a command, the name of a routine, the name of a file, or the abbreviation for a system privilege.                                                                                                                                                                                                             |  |

| Monospace text     | Monospace type indicates code examples and interactive screen displays.                                                                                                                                                                                                                                                                |  |

|                    | In the C programming language, monospace type in text identifies the following elements:keywords, the names of independently compiled external functions and files, syntax summaries, and references to variables or identifiers introduced in an example.                                                                             |  |

| -                  | A hyphen at the end of a command format description, command line, or code line indicates that the command or statement continues on the following line.                                                                                                                                                                               |  |

| numbers            | All numbers in text are assumed to be decimal unless otherwise noted.<br>Nondecimal radixes—binary, octal, or hexadecimal—are explicitly indicated.                                                                                                                                                                                    |  |

# **Chapter 1. Introduction**

This manual is divided into two parts: the first, which discusses changes to privileged code on OpenVMS Alpha to support 64-bit addressing and kernel threads; and the second, which discusses the changes necessary to privileged code and to OpenVMS physical infrastructure to support the OpenVMS operating system on the Intel ® Itanium ® architecture.